#### METROLOGY AND MEASUREMENT SYSTEMS

Index 330930, ISSN 0860-8229 www.metrology.wat.edu.pl

# HIGH-PRECISION 3-CHANNEL TIME INTERVAL COUNTER IN A LOW-COST AMD SPARTAN-7 FPGA

Ryszard Szplet<sup>1)</sup>, Paweł Kwiatkowski<sup>1)</sup>, Krzysztof Różyc<sup>1)</sup>, Dominik Sondej<sup>1)</sup>, Zbigniew Jachna<sup>1)</sup>, Jakub Tyburski<sup>1)</sup>, Paweł Ślązak<sup>1)</sup>, Albin Czubla<sup>2)</sup>, Piotr Szterk<sup>2)</sup>

- 1) Military University of Technology, Faculty of Electronics, Institute of Telecommunication, ul gen. Sylwestra Kaliskiego 2, 00-908 Warsaw, Poland ( dominik.sondej@wat.edu.pl)

- 2) Division of Time and Length, Central Office of Measures, ul. Elektoralna 2, 00-139 Warsaw, Poland

#### **Abstract**

This paper presents the design, implementation, and performance evaluation of a 3-channel integrated time interval counter implemented in a low-cost Spartan-7 (AMD/Xilinx) FPGA device. Based on a hybrid measurement approach that combines timestamping and two-stage interpolation, the proposed solution provides high metrological parameters, such as: time resolution (2 ps), measurement precision (better than 8 ps) and range (up to 1 h). To achieve high resolution and reduce nonlinearity of the time-to-digital converters (TDCs) involved, the multi-edge coding in four independent tapped delay lines (TDL) was applied. An improved encoder eliminates bubble errors and compresses raw TDL data with limited logic overhead. The integrated code processor performs real-time calibration based on the Statistical Code Density Test (SCDT). Implemented within a low-end FPGA chip, the time counter occupies approximately one-third of available logic resources and consumes around 0.5 W. Experimental evaluation confirms the system's potential for cost-effective, high-performance time interval measurements in portable instrumentation.

**Keywords**: time interval measurement, time interval counter, time-to-digital converter (TDC), field-programmable gate array (FPGA).

#### 1. Introduction

Precise time interval and frequency measurements are important in an expanding range of applications, including the creation and distribution of stable time scales, navigation systems, and high-energy physics experiments [1-3]. The requirements on time counters are also constantly increasing. However, due to these high requirements, the number of high-precision measurement instruments available is very limited. The offer is dominated by large, energy-consuming and expensive desktop time counters [4-7]. As a supplementary proposal, just a few portable counters appear [8-10]. These counters not only match the former ones in terms of high metrological parameters, but they are also pocket-sized, consume little energy, are easy to use and much cheaper. Consequently, these devices have garnered significant interest and are now widely adopted in professional time and frequency laboratories. Advances in microelectronics further enable the replacement of large stationary counters with smaller, portable alternatives boasting superior parameters.

The measurement core of many modern time interval counters is based on *field-programmable gate arrays* (FPGAs). These programmable logic devices provide high flexibility, low cost, and rapid deployment while maintaining relatively high performance. To achieve high resolution and precision across a broad measurement range, FPGA-based counters often incorporate the interpolation method with high-resolution *time-to-digital converters* (TDCs) [2, 3]. Among many time-to-digital conversion techniques, *tapped delay line* (TDL)

based solutions remain prevalent and continue to be adapted for newer FPGA chips [11-13]. While mainstream FPGAs offer increasingly extensive logic resources, many dedicated functional blocks remain underutilized in time interval measurement systems. Users often pay extra cost for faster chips with surplus logic capacity, which increases power consumption and design complexity. This has driven efforts to maximize performance of time interval measurement systems implemented in small, low-cost FPGAs [14–17].

In this paper, we propose a 3-channel integrated time interval counter implemented in a compact, low-cost AMD/Xilinx Spartan-7 FPGA device. By leveraging state-of-the-art TDC techniques, we demonstrate that high-performance time-interval measurement systems can be realized in programmable logic devices, enabling their practical deployment in pocket-sized instruments.

#### 2. Measurement method

An easy way to measure time intervals is the counting of the reference clock periods of a known frequency. The higher the frequency, the better the measurement resolution is achieved. If the binary counter operates continuously and the occurrence of an event (in the form of an edge of an electrical signal) does not cause it to start or stop, but only to register its current state (N), then it is called the timestamping method. In such a solution, the period counter can be shared by multiple channels to form a common, coarse timescale for recording events. This allows to specify time intervals between any registered *timestamps* (TS). Although the method provides great flexibility and a wide measurement range, its resolution is limited by the clock signal period  $(T_{clk})$ . In practice, it is limited to nearly 1 ns for the newest FPGAs families. To reduce dynamic power consumption, the clock frequency in the proposed design must be additionally decreased. TDCs are known to achieve several orders of magnitude better resolution, but have a limited measurement range. The advantages of both solutions are combined in the interpolation method [18].

# 2.1. Timestamps and two-stage interpolation

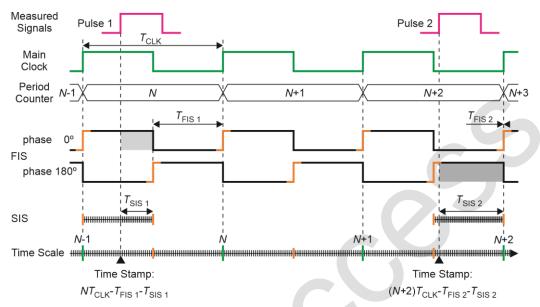

The operation of a timestamp and two-stage interpolation-based counter is illustrated in Fig. 1. The TDC measures the interval ( $T_{\rm TDC}$ ) between an input pulse rising edge and the nearest rising edge of the main clock signal. The *first interpolation stage* (FIS) determines whether the event occurred in the first half (0° phase) or second half (180° phase) of the clock period ( $T_{\rm FIS}$ ). This reduces the operating range of the *second interpolation stage* (SIS) by half. Thus, the SIS can quantizes the time interval within half the clock period ( $T_{\rm SIS}$ ) with picosecond-level precision and reduced logic resource usage. The final TS value is calculated as:

$$TS = N \times T_{CLK} - T_{FIS} - T_{SIS}. \tag{1}$$

While multi-stage in-period interpolation (e.g., two-stage) complicates counter design [19], it can drastically reduce logic resource consumption. With multi-stage interpolation also lower frequency clock can be used. Both of these aspects result in reduced power consumption, which is essential for pocket-sized devices.

### 2.2. Multi-edge coding in independent coding lines

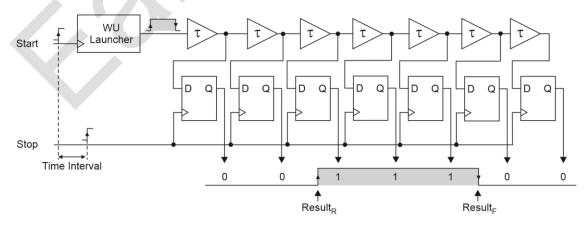

A common TDC architecture employs a *time coding line* (TCL), which combines a TDL with a register (Fig. 2). A single delay buffer connected to a *flip-flop* (FF) is called here a delay cell. The start signal propagates through the TDL, reaching successive FF inputs with a delay proportional to the buffer's propagation time ( $\tau$ ), while the stop signal captures the TDL's state

in the register. In FPGAs, such design is often implemented using carry chains [3], which minimize interconnection delays but suffer from significant nonlinearity. The delay introduced by a single delay cell (referred to as bin size) can vary from a few to tens of picoseconds due to factors such as technological spread, FPGA granularity, inhomogeneities in the clock signal distribution network, metastability, and *process-voltage-temperature* (PVT) variations.

Fig. 1. Measurement method – timestamps with two-stage interpolation.

To mitigate this nonlinearity and improve resolution beyond the average delay line resolution  $(\tau)$ , two methods are often adopted: the multi-TCL method [20, 21] and the wave union method [22]. Identical TCLs implemented on the same FPGA device exhibit unique transfer functions due to intrinsic delay variations, enabling them to be treated as independent measurement units. Results from multiple TCLs can be averaged or algorithmically fused (e.g., [23]) to enhance resolution. In the WU method, a pulse generator (WU Launcher) initiates multiple pulses to propagate along the TDL upon detecting a start signal edge, which is shown in Fig. 2. This creates multiple logic transitions ('0' to '1' and '1' to '0') in the register, enabling multi-edge coding. If one pulse edge encounters a large bin, another edge may intersect a narrower bin, statistically improving resolution and precision.

Fig. 2. Wave Union (WU) TDC.

The multiple TCL method requires considerable logic resources while the WU method is more difficult to implement and requires a complex encoder to identify transitions. In particular, the more edges are generated by the WU Launcher, the longer the TDL and the more complex the encoder must be. However, these methods can be combined to achieve significant improvements in TDC performance while minimizing system complexity and this is known as multi-edge coding in independent TCLs [24].

## 3. Integrated time interval counter

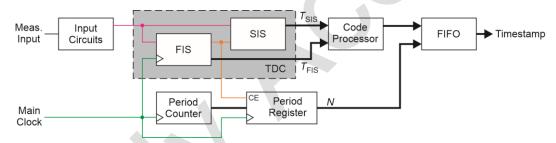

A block diagram of a single measurement channel of the designed integrated time counter, which combines timestamping and interpolation methods, is shown in Fig. 3. The input circuit consists of a D-type FF that sets a high logic state at the output upon the rising edge of the measurement signal and maintains it until the end of conversion process. A two-stage TDC measures the time interval within a single main clock period. First, the FIS identifies the main clock signal phase (0° or 180°) and generates a phase-synchronized pulse. Then, the SIS accurately measures the time interval between the edge of the measurement signal and the phase-synchronized edge produced by the FIS. This synchronized pulse is also used to latch the current state of the period counter into a period register. The period counter is implemented as a 40-bit binary counter, driven by a 300 MHz main clock. As a result, it provides a measuring range of up to one hour before overflowing. Raw results from the FIS and SIS are processed in the code processor, which performs the following functions: (1) compresses the obtained results (*T*<sub>FIS</sub>, *T*<sub>SIS</sub>), (2) executes calibration procedures to identify the TDC transfer function, (3) calculates values of timestamps based on calibration results. Final results are stored in a *first-in first-out* (FIFO) memory.

Fig. 3. Single measurement channel of the integrated time interval counter.

### 3.1. Time-to-digital converter design

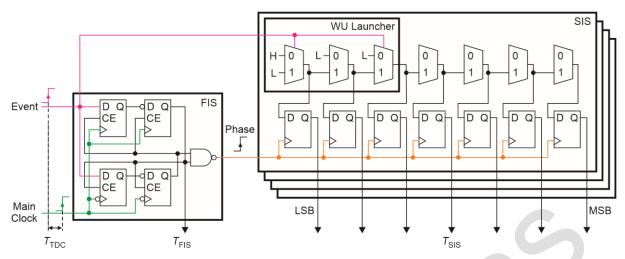

The design module that largely determines the performance of the integrated time interval counter is the TDC, which design is shown in Fig. 4. The FIS consists of two double-synchronizers clocked on opposite edges of the clock signal. These synchronizers minimize the probability of metastable states and are interconnected via *clock enable* (CE) signals. In the idle state, both synchronizers produce a logic '1' at the output, setting the phase signal to '0'. If one of the synchronizers detects a high logic level at its input, it disables the operation of the other and triggers a transition on the phase signal. This edge is subsequently used to latch the current state of the TDL in the SIS.

The TDL is implemented using carry-chain multiplexers, which provide the shortest propagation delay among all FPGA components due to their optimized internal structure and direct routing paths that bypass general-purpose switching matrices. The WU launcher consists of 20 multiplexers, all configured (except the last one) to output a high logic level. A transition on the phase signal toggles the first and last multiplexers, generating a single pulse that propagates along the TDL. The pulse width is proportional to the number of multiplexers and their propagation delays. Such design enables precise control over the WU pattern while minimizing logic resource usage when integrating the TDL and launcher.

Fig. 4. Two-stage TDC design.

The complete TDL comprises 148 carry-chain multiplexers. However, due to the presence of the WU launcher, only 128 are used for the first edge. Assuming an average propagation delay ( $\tau$ ) of approximately 16 ps per multiplexer in the Spartan-7 FPGA (speed grade -2), the SIS measurement range is slightly over 2 ns (~2.048 ns). Given the main clock frequency of 300 MHz and the use of a two-phase clock in the FIS, this allows coverage of half the clock period (1.66 ns) while leaving a safety margin for clock phase mismatches and PVT variations.

Proper distribution of the clock signal to the FFs is crucial for the correct operation of the converter. In the TDC, two clock signals are used: the main 300 MHz clock (marked green in Fig. 4), which is delivered to the FIS, and a clock signal generated by the FIS (marked orange in Fig. 4), which drives the FFs in the SIS. Both signals are distributed within the FPGA using dedicated clock routing paths, which limits clock skew to tens of picoseconds [25, 26]. The selection of the active clock edge takes place directly at the clock input of the FFs.

The described WU-based TDL is replicated in the described TDC four times. With two-edge encoding applied across four independent TDLs, the overall measurement resolution improves by a factor of eight compared to a classic TDL (*i.e.*, a single TDL connected to a register). Additionally, the encoding of results is simplified, as discussed in the next subsection. Such configuration generates  $4 \times 148$  bits of raw data, where the position of eight transitions is critical to determining the time interval ( $T_{\rm SIS}$ ). Consequently, data compression (encoding) is the first processing step, followed by conversion of the compressed data into a time value. Both operations are performed by the code processor.

## 3.2. TDC encoding and code processing

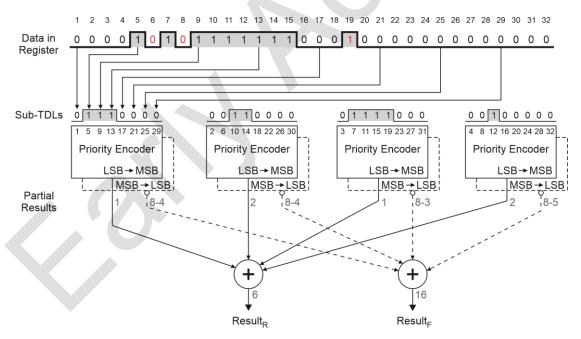

The first task of the code processor is data compression, accomplished by an encoder. The encoder identifies the positions in the SIS data where logic state transitions occur and then derives a single compressed value from multiple transitions across multiple lines. The structure and operating principle of the encoder are presented in Fig. 5.

In TDCs employing TDL architectures, a common issue is the occurrence of bubble errors. These errors arise when the measured time interval corresponds to a region in the delay line where the transition between logic states is not a clean, single-step boundary. Instead, discontinuities appear in the thermometric code due to timing mismatches, noise, or metastability in the delay elements (in Fig. 5 such errors are marked in red in the data from a single SIS register). A simple and effective solution is to virtually decompose the result into partial results (sub-TDLs) [27, 28]. Each sub-TDL consists of every *k*-th bit from the original TDL result, where the value of *k* is chosen based on the maximum number of bits over which

a bubble error can occur (four in this work). Following this decomposition, each sub-TDL is free of bubble errors. This method is straightforward in its implementation - requiring only the re-routing of certain signals - and highly effective, as it virtually eliminates all bubble errors.

Once the results are free of bubble errors, the encoder searches for the transitions '0'-'1' and '1'-'0'. Identifying multiple edges can be relatively complex [29, 30]. Therefore, we have limited the process to only two edges per TDL. These edges are identified by two priority encoders operating in opposite directions: one from the *most significant bit* (MSB) to the *least significant bit* (LSB) and the other in reverse. This approach significantly simplifies the data encoding process. The longer the time interval, the higher the value of the '0'-'1' transition position and the lower the value of the '1'-'0' transition position. Consequently, the output from the MSB-to-LSB priority encoder is inverted (converted to one's complement code). Finally, the results from both transitions, obtained from all four WU-based TDLs, are summed together.

In the next step, the code processor translates the values obtained from the FIS and SIS into the time values. This translation is performed using built-in *block random access memory* (BRAM), which stores the transfer characteristics of the interpolators, and results in numerical outputs representing fractions of a clock period with sub-picosecond resolution (3.33 ns /  $2^{14} \approx 0.2$  ps). Additionally, the code processor incorporates algorithms for updating the transfer characteristics during the calibration process, based on the *statistical code density test* (SCDT) [31]. Calibration is initiated automatically at each system start-up or manually upon user request. This approach enables the device to maintain high measurement precision under varying environmental conditions. The hardware implementation of the calibration algorithms brings several benefits: reduced calibration time, lower data transfer requirements to the host computer, and simplified control software [32].

Fig. 5. Block diagram and operation principle of the SIS encoder.

## 3.3. Integrated time counter implementation

The integrated time interval counter was implemented in a mid-sized *Spartan-7* (XC7S50) FPGA device from AMD/Xilinx. Spartan-7 chips are among the simplest and smallest in the 7 series, notably lacking gigabit transceivers and a PCI interface. This minimalistic design contributes to their low cost and low power consumption but they are also a bit slower than other

AMD/Xilinx chips like Artix, Kintex or Virtex devices. Nevertheless, Spartan-7 FPGAs provide sufficient resources and capabilities for implementing high-performance time interval counters.

Each measurement channel was implemented within a single clock region. Special care was taken to precisely locate the FIS within the programmable array – the two synchronizers were positioned in close proximity, and the routing paths to the NAND gate were manually aligned. This careful placement was essential to ensure that both phases of the clock signal remained equal and that good synchronization with the SIS was maintained.

Table 1 summarizes the logic resource utilization of the counter in the Spartan-7 FPGA. Overall, the complete design occupies about one-third of the available programmable logic blocks (Slices) on the chip. Approximately half of the consumed resources (including Slices, *look-up tables* LUTs, and FFs) are used by the SIS and encoder (a part of the code processor), which are duplicated across three channels. If only a single-stage interpolation with TDC based on two-edge coding across four independent lines were used, the TDL length would need to be doubled in order to cover the main clock period, significantly increasing resource consumption. BRAM module is employed to store the TDC transfer characteristics and to implement a FIFO memory, which buffers timestamps before they are sent to the control computer via a USB interface. Additionally, the counter integrates several other controllers for the external frequency synthesizer, calibrator, USB interface, and other peripherals. These modules involve additional use of logic resources.

|              | Slice      | LUT        | LUTRAM | FF         | BRAM   |

|--------------|------------|------------|--------|------------|--------|

| Available    | 8150       | 32600      | 9600   | 65200      | 75     |

| FIS (×3)     | 2 (6)      | 3 (9)      | 0      | 4 (12)     | 0      |

| SIS (×3)     | 148 (444)  | 0          | 0      | 592 (1776) | 0      |

| Encoder (×3) | 342 (1026) | 953 (2859) | 0      | 594 (1782) | 0      |

| Full design  | 2885       | 6819       | 229    | 7233       | 15.5   |

| Utilization  | 35.4 %     | 20.9 %     | 2.4 %  | 11.1 %     | 20.7 % |

Table 1. A summary of logic resource utilization of the integrated time interval counter.

Table 2 presents the current consumption of the designed integrated time interval counter, focusing on the FPGA chip only. While the 300 MHz main clock drives the period counter, register, and FIS (in all three channels), the remaining modules operate under a 100 MHz system clock. The complete timestamp processing - from raw data acquisition to the final time value - introduces a dead time of approximately 40 ns per measurement channel, corresponding to a maximum measurement repetition rate of 25 MSa/s per channel. Based on these parameters, the power estimates were obtained using the Vivado software tool. The total estimated current consumption was 135 mA, corresponding to a power consumption of approximately 181 mW (assuming a typical core voltage), with a medium confidence level. To verify these values, 25 MHz signals were connected to all three input channels, and the current consumption was measured using a USB tester FNB58 from FNIRSI. The actual current consumption was slightly lower - around 113 mA - but since it was drawn from a 5 V USB supply, the measured power consumption amounted to approximately 565 mW.

The supply voltage, and particularly its noise, has a significant impact on the performance of the integrated time counter. Due to high noise levels caused by the switching nature of the computer's power supply, linear voltage regulators were implemented in the module's power paths. In addition to an LC input filter, multi-stage linear regulation was used to minimize supply noise. As a result, the current drawn from the 5 V USB source matches the total current consumed by the counter at various voltages from 1 V to 3.3 V. This additional power loss reduces efficiency but is necessary to maintain measurement precision.

|         |         | Estimated    |            | Measured     |            |

|---------|---------|--------------|------------|--------------|------------|

|         |         | Current [mA] | Power [mW] | Current [mA] | Power [mW] |

| Dynamic | Clocks  | 31           | 31         |              |            |

|         | Signals | 14           | 14         |              |            |

|         | Logic   | 12           | 12         |              |            |

|         | BRAM    | 22           | 22         | 67           | 335        |

|         | I/O     | 9            | 25         |              |            |

|         | XADC    | 1            | 2          |              |            |

|         | Total   | 89           | 106        |              |            |

| Static  |         | 46           | 75         | 46           | 230        |

| Total   |         | 135          | 181        | 113          | 565        |

Table 2. A summary of power consumption of the integrated time interval counter.

#### 4. Test results

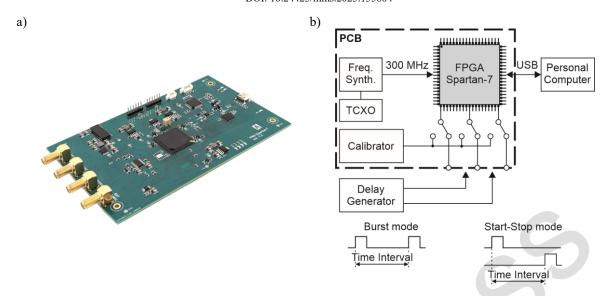

The designed interpolated time counter was tested using a custom-built prototype *printed* circuit board (PCB), shown in Fig. 6(a). The board features four signal inputs with an input impedance of 50  $\Omega$ . Three of these inputs are dedicated to recording input events and support an input voltage range of  $\pm 5$  V, with an adjustable threshold voltage in 1 mV steps. Each of these inputs can also be optionally configured to accept an external trigger signal. The counter includes an onboard TCXO that provides a 10 MHz reference clock with a stability of  $2\times10^{-8}$ . Alternatively, an external high-stability clock source (e.g., an atomic clock with a maximum signal level of 1 Vrms) can be connected via the fourth SMA input. One of these clock sources is used as the reference clock for the onboard frequency synthesizer, which generates the 300 MHz main clock for the integrated time counter. The board is powered and controlled via a USB 3.0 interface, which also supports the USB Power Delivery protocol.

## 4.1. Test setup

Figure 6(b) presents the test setup used to characterize the parameters of the developed time interval counter. The on-board calibrator generates a square-wave signal which, for the purposes of calibration procedures (SCDT), is connected to the integrated time counter instead of the measurement signals. Test time intervals are generated with the use of the Model 745 digital delay generator from Berkeley Nucleonics [33].

Parameters of the counter were evaluated in two modes: burst and start-stop. In the burst mode, the time intervals are defined by the rising edges of two consecutive pulses of a square signal applied to a single counter input. Thus, the measurement is performed on one selected channel. In the start-stop mode, the start pulse is applied to one counter input while the stop pulse is attached to the another one, resulting in an inter-channel measurement. The counter configuration and data transfer are managed via a USB interface. All tests were conducted under laboratory conditions, at an ambient temperature of approximately 21°C.

Fig. 6. (a) The prototype PCB with the integrated time interval counter and (b) the test setup.

# 4.2. Resolution and nonlinearity

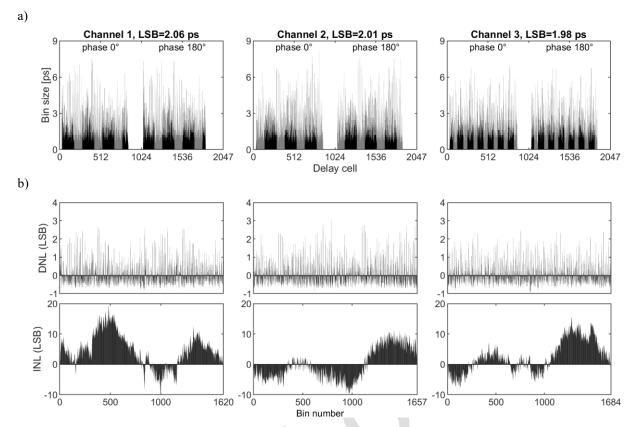

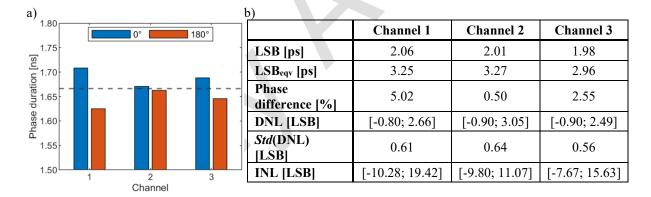

On start-up or on demand, the code processor initiates a calibration procedure based on the SCDT. A square-wave signal from the calibrator - uncorrelated with the main clock - is used as a source of random time intervals for the TDC. The counter collects 2 million random samples, based on which the probability of occurrence of various digital codes in the TDC is calculated. By multiplying the obtained probabilities by the TDC measurement range, the actual bin sizes are determined. The results for all three measurement channels are presented in Fig. 7(a). These characteristics reveal a split between the results obtained from the SIS during the first  $(0^{\circ})$  and second (180°) phases of the main clock signal. In every case, the resolution, defined as the size of LSB, is approximately 2 ps (only nonzero bins are taken into account). However, distinct differences exist between individual delay cells. These differences are illustrated in the differential nonlinearity (DNL) and integral nonlinearity (INL) plots shown in Fig. 7(b), where digital codes that never occur have been omitted and only nonzero bins are considered. Taking into account both the quantization error and the nonlinearities, it can be estimated that the designed two-stage TDC behaves like an ideal TDC (DNL = 0 LSB) with an equivalent resolution of about 3.0–3.3 ps [7]. Due to the code processor, which computes the measurement result based on the actual transfer characteristics, the influence of nonlinearities on the precision is significantly reduced.

From the SCDT results, phase uniformity can also be determined. Fig. 8(a) shows the differences between durations of the 0° and 180° phases. The phase of the clock signal is selected by a multiplexer in the programmable logic block, where the clock signal is routed to the FF through either a buffer or an inverter. The difference in durations of these phases is mainly attributed to the disparate propagation times of these two elements, along with process variations and clock skew. In the end, the two phases differ by up to a few percent (up to 5%, equivalent to 83.6 ps), which increases the required measurement range in the SIS. A summary of the resolution and nonlinearity of the counter is provided in Fig. 8(b).

Fig. 7. (a) Results of the SCDT with bin sizes and (b) nonlinearity plots (DNL and INL).

Fig. 8. (a) Phase uniformity and (b) a summary of the TDC nonlinearity.

## 4.3. Precision

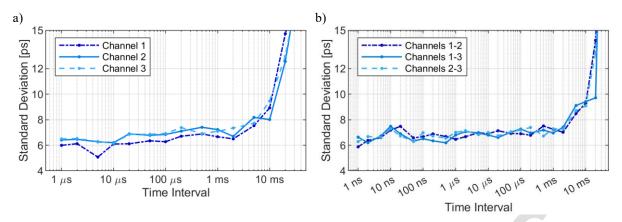

The precision of the integrated time interval counter was evaluated by recording an arbitrarily selected set of 2000 timestamps, either in a single channel (burst mode) or across two channels (start-stop mode). This yielded 1000 time interval measurements, swept from 1 ns to 50 ms. In burst mode, the lower bound of the measurement range (1  $\mu$ s) was limited by the capabilities of the delay generator. Precision was calculated as the standard deviation of the 1000 measured time intervals between start and stop pulses.

In both operating modes and across various channel configurations, the counter maintained a precision better than 8 ps within a measurement range of up to 2 ms. Considering that each time interval is determined from two timestamps, the estimated single-shot precision is better than 5.65 ps, which proves the high performance obtained in a low-cost FPGA chip.

Fig. 9. Integrated time interval counter precision (a) in the burst mode, (b) in the start-stop mode.

#### 5. Conclusions

This work demonstrates that precise, multi-channel time interval measurements can be achieved using compact and inexpensive FPGA devices. The proposed time counter, implemented in a Spartan-7 (AMD/Xilinx) programmable device, successfully integrates a timestamping method with a two-stage interpolation based on an enhanced TDC architecture. The use of multi-edge coding in four independent TDLs and an efficient encoder provides high resolution while minimizing resource utilization. The developed counter, conveniently controlled and powered via a single USB port, achieves an equivalent resolution of approximately 3 ps and a single-shot precision better than 5.65 ps, with a measurement range extending up to one hour. These high metrological parameters are achieved with relatively low power consumption of 0.5 W. The presented results confirm the practicality of deploying advanced time measurement solutions in cost-sensitive and space-constrained applications, such as portable low-power instruments that can effectively compete with expensive desktop devices in many areas, *e.g.*, clock monitoring, time and frequency distribution, as well as in various physical and technical experiments.

# Acknowledgements

Research financed from state budget funds, allocated by the Minister of Science under the Polish Metrology II program, contract no. PMII/SP/0056/2024/02.

# References

- [1] Henzler, S. (2010). Time-to-Digital Converters. In *Springer series in advanced microelectronics* (pp. 123). Springer. <a href="https://doi.org/10.1007/978-90-481-8628-0">https://doi.org/10.1007/978-90-481-8628-0</a>

- [2] Szplet, R. (2014). Time-to-Digital Converters. In *Design, modeling and testing of data converters* (pp. 211-246). Springer. https://doi.org/10.1007/978-3-642-39655-7

- [3] Szyduczyński, J., Kościelnik, D., & Miśkowicz, M. (2023). Time-to-digital conversion techniques: a survey of recent developments. *Measurement*, 214, 112762. https://doi.org/10.1016/j.measurement.2023.112762

- [4] Keysight Technologies. (2016), 53200A Series RF/Universal Frequency Counter/Timers. [DataSheet]. https://www.keysight.com/us/en/assets/7018-02642/data-sheets/5990-6283.pdf

- [5] Stanford Research Systems. (2025), *Model SR620. Universal Time Interval Counter*. [Datasheet Rev. 2.9]. <a href="https://www.thinksrs.com/downloads/pdfs/manuals/SR620m.pdf">https://www.thinksrs.com/downloads/pdfs/manuals/SR620m.pdf</a>

- [6] Pendulum Instruments. (2025), CNT-104R Multi-channel Frequency Analyzer. [Datasheet eev.22]. <a href="https://pendulum-instruments.com/wp-content/uploads/2025/04/CNT-104S-Datasheet.pdf">https://pendulum-instruments.com/wp-content/uploads/2025/04/CNT-104S-Datasheet.pdf</a>

- [7] Szplet, R., Kwiatkowski, P., Różyc, K., Jachna, Z., & Sondej, T. (2017). Picosecond-precision multichannel autonomous time and frequency counter. *Review of Scientific Instruments*, 88(12). https://doi.org/10.1063/1.4997244

- [8] Marvin Test Solutions. (2023). *GC2200 Series*. [Datasheet Rev. C]. <a href="https://www.marvintest.com/Product/GC2200-Series">https://www.marvintest.com/Product/GC2200-Series</a>

- [9] PikTime Systems. *Time/Frequency Counter Model T3200U*. [Leaflet]. https://piktime.com/images/PIKTIME/T3200U%20ulotka.pdf?1742549657861

- [10] Corna, N., Garzetti, F., Lusardi, N., & Geraci, A. (2021). Digital instrument for time Measurements: Small, Portable, High–Performance, Fully programmable. *IEEE Access*, 9, 123964–123976. <a href="https://doi.org/10.1109/access.2021.3109155">https://doi.org/10.1109/access.2021.3109155</a>

- [11] Xie, W., Chen, H., & Li, D. D. (2021). Efficient Time-to-Digital Converters in 20 nm FPGAs With Wave Union Methods. *IEEE Transactions on Industrial Electronics*, 69(1), 1021–1031. <a href="https://doi.org/10.1109/TIE.2021.3053905">https://doi.org/10.1109/TIE.2021.3053905</a>

- [12] Qi, X., Zhang, J., & Wang, Y. (2024). Realization of zero measurement dead time on FPGA-based Time-to-Digital converters. *IEEE Transactions on Instrumentation and Measurement*, 74, 2001008. https://doi.org/10.1109/TIM.2024.3509597

- [13] Mścichowski, M., & Kwiatkowski, P. (2025). Hybrid ALM-DSP TDC in Intel Arria 10 FPGA. *Measurement*, 240, 115523. https://doi.org/10.1016/j.measurement.2024.115523

- [14] Zheng, J., Cao, P., Jiang, D., & An, Q. (2017). Low-Cost FPGA TDC with high resolution and density. IEEE Transactions on Nuclear Science, 64(6), 1401–1408. <a href="https://doi.org/10.1109/tns.2017.2705802">https://doi.org/10.1109/tns.2017.2705802</a>

- [15] Tontini, A., Gasparini, L., Pancheri, L., & Passerone, R. (2018). Design and characterization of a Low-Cost FPGA-Based TDC. *IEEE Transactions on Nuclear Science*, 65(2), 680–690. <a href="https://doi.org/10.1109/TNS.2018.2790703">https://doi.org/10.1109/TNS.2018.2790703</a>

- [16] Dadouche, F., Turko, T., Uhring, W., & Le, J.-P. (2018). New Design-methodology of High-performance TDC on a Low Cost FPGA Targets. *Sensors and Transducers*, 193(10), 123–134. <a href="https://www.sensorsportal.com/HTML/DIGEST/october\_2015/Vol\_193/P\_2745.pdf">https://www.sensorsportal.com/HTML/DIGEST/october\_2015/Vol\_193/P\_2745.pdf</a>

- [17] O'Flynn, C. (2023). PicoEMP: a Low-Cost EMFI platform compared to BBI and voltage fault injection using TDC & external VCC measurements (pp. 60–71). 2023 Workshop on Fault Detection and Tolerance in Cryptography (FDTC). https://doi.org/10.1109/fdtc60478.2023.00015

- [18] Nutt, R. (1968). Digital Time Intervalometer. Review of Scientific Instruments, 39(9), 1342–1345. https://doi.org/10.1063/1.1683667

- [19] Jansson, J., Mantyniemi, A., & Kostamovaara, J. (2008). Synchronization in a multilevel CMOS Time-to-Digital converter. IEEE Transactions on Circuits and Systems I Regular Papers, 56(8), 1622–1634. https://doi.org/10.1109/tcsi.2008.2010111

- [20] Szplet, R., Jachna, Z., Kwiatkowski, P., & Rozyc, K., (2013). A 2.9 ps equivalent resolution interpolating time counter based on multiple independent coding lines. *Measurement Science and Technology*, 24(3). <a href="https://iopscience.iop.org/article/10.1088/0957-0233/24/3/035904">https://iopscience.iop.org/article/10.1088/0957-0233/24/3/035904</a>

- [21] Frankowski, R., Gurski, M., & Szplet, R. (2024). Kintex Ultrascale's multi-segment digital tapped delay lines with controlled characteristics for precise time-to-digital conversion. *Metrology and Measurement Systems*, 31(2), 417–429. <a href="https://doi.org/10.24425/mms.2024.149697">https://doi.org/10.24425/mms.2024.149697</a>

- [22] Wu, J., & Shi, Z. (2008). The 10-ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay. *IEEE Nuclear Science Symposium Conference Record*. <a href="https://doi.org/10.1109/nssmic.2008.4775079">https://doi.org/10.1109/nssmic.2008.4775079</a>

- [23] Sondej, D., Szymanowski, R., & Szplet, R. (2021). Methods of precise determining the transfer function of picosecond time-to-digital converters. *Metrology and Measurement Systems*, 539–549. https://doi.org/10.24425/mms.2021.137697

- [24] Szplet, R., Sondej, D., & Grzeda, G. (2016). High-Precision Time Digitizer based on Multiedge Coding in Independent Coding Lines. *IEEE Transactions on Instrumentation and Measurement*, 65(8), 1884–1894. <a href="https://doi.org/10.1109/tim.2016.2555218">https://doi.org/10.1109/tim.2016.2555218</a>

- [25] Fishburn, M.W., Menninga, L.H., Favi, C., & Charbon, E. (2013). A 19.6 ps, FPGA-Based TDC With Multiple Channels for Open Source Applications. *IEEE Transactions on Nuclear Science*, 60(3), 2203–2208. <a href="https://doi.org/10.1109/TNS.2013.2241789">https://doi.org/10.1109/TNS.2013.2241789</a>

- [26] Kwiatkowski, P., & Szplet, R. (2020). Efficient Implementation of Multiple Time Coding Lines-Based TDC in an FPGA Device. *IEEE Transactions on Instrumentation and Measurement*, 69(10), 7353–7364. https://doi.org/10.1109/TIM.2020.2984929

- [27] Song, Z., Wang, Y., & Kuang, J. (2018). A 256-channel, high throughput and precision time-to-digital converter with a decomposition encoding scheme in a Kintex-7 FPGA. *Journal of Instrumentation*, *13*(05), P05012. <a href="https://doi.org/10.1088/1748-0221/13/05/p05012">https://doi.org/10.1088/1748-0221/13/05/p05012</a>

- [28] Chen, H., & Li, D. D. (2018). Multichannel, Low Nonlinearity Time-to-Digital Converters Based on 20 and 28 nm FPGAs. *IEEE Transactions on Industrial Electronics*, 66(4), 3265–3274. <a href="https://doi.org/10.1109/tie.2018.2842787">https://doi.org/10.1109/tie.2018.2842787</a>

- [29] Wang, Y., Zhou, X., Song, Z., Kuang, J., & Cao, Q. (2019). A 3.0-ps rms Precision 277-MSamples/s Throughput Time-to-Digital Converter Using Multi-Edge Encoding Scheme in a Kintex-7 FPGA. *IEEE Transactions on Nuclear Science*, 66(10), 2275–2281. https://doi.org/10.1109/tns.2019.2938571

- [30] Kwiatkowski, P., Sondej, D., & Szplet, R. (2023). Subpicosecond resolution time interval counter with multisampling wave union type B TDCs in 28 nm FPGA device. *Measurement*, 209, 112510. <a href="https://doi.org/10.1016/j.measurement.2023.112510">https://doi.org/10.1016/j.measurement.2023.112510</a>

- [31] Cova, S., Bertolaccini, M. (1970). Differential linearity testing and precision calibration of multichannel time sorters, *Nuclear Instruments and Methods*, 77(2), 269–276. <a href="https://doi.org/10.1016/0029-554x(70)90095-9">https://doi.org/10.1016/0029-554x(70)90095-9</a>

- [32] Szplet, R., Kalisz, J., & Jachna, Z. (2009). A 45 ps time digitizer with two-phase clock and dual-edge two-stage interpolation in FPGA device. *Measurement Science and Technology*, 20(2), 025108. <a href="https://doi.org/10.1088/0957-0233/20/2/025108">https://doi.org/10.1088/0957-0233/20/2/025108</a>

- [33] Model 745-OEM 4/8 Channel Pulse & Delay Generator, *Berkeley Nucleonics Data Sheet*, <a href="https://www.berkeleynucleonics.com/sites/default/files/products/resources/model\_745-oem\_datasheet\_november\_2020\_0.pdf">https://www.berkeleynucleonics.com/sites/default/files/products/resources/model\_745-oem\_datasheet\_november\_2020\_0.pdf</a>

Ryszard Szplet received the M.Sc. degree in electronic engineering and the Ph.D. and Habilitation degrees in applied sciences from the Military University of Technology (MUT), Warsaw, Poland, in 1989, 1997, and 2013, respectively. From 2000 to 2001, he spent one year as a researcher with the University of Oulu, Oulu, Finland. He is currently Full Professor with the MUT (title obtained in 2019), where he

also heads the research team of precise time metrology. In the years 2020-2024 he held the position of Dean of the Faculty of Electronics at the MUT. He is a member of the Committee on Metrology and Scientific Instrumentation of the Polish Academy of Sciences (PAS). He also serves as Editor-in-chief of the international journal Metrology and Measurement Systems. He has been involved in various research projects, sponsored by public and private funds. He has authored or coauthored over 150 papers appearing in international journals and conference proceedings. His current research interests include fast digital electronics as well as methods and techniques for precise time metrology, especially instrumentation for advanced time interval and frequency measurements.

Pawel Kwiatkowski received the B.Sc. and M.Sc. degrees in Electronics and Communication Engineering, and the Ph.D. degree in Applied Science from the Military University of Technology (MUT), Warsaw, Poland, in 2010, 2011, and 2016, respectively. He is currently an Assistant Professor at MUT. In 2022, he was awarded the Scholarship of the Minister of Education and Science of the Republic of Poland for outstanding

young scientists. He serves as an Associate Editor for the IEEE Transactions on Instrumentation and Measurement. His research focuses on the design and development of methods and systems for time metrology, particularly time-to-digital converters (TDCs)

and time/frequency counters, implemented using field-programmable gate arrays (FPGAs).

Krzysztof Różyc is a researcher in the Faculty of Electronics at the Military University.of Technology He received his Bsc in 1999, and Msc in 2008. He specializes in design and testing of advanced timing instrumentation, especially for precise generation, measurement, and distribution of time intervals.

Dominik Sondej received the M.Sc. and Ph.D. degrees in Electronic and Communication Engineering from the Military University of Technology (MUT), Warsaw, Poland, in 2012 and 2019, respectively. He is currently an Assistant Professor at the Faculty of Electronics of MUT, where he is involved in teaching, research, and supervision of diploma and doctoral theses. His scientific interests focus on

time and frequency metrology, time-to-digital and frequency-to-digital converters, embedded systems, as well as low-power biomedical signal processing. He has also contributed to research on cryptographic hardware security, including side-channel analysis. Dr. Sondej is a member of the Editorial Board of the international journal Metrology and Measurement Systems published by the Polish Academy of Sciences. He also serves as a reviewer for scientific journals and conferences in the fields of electronics and metrology.

Zbigniew Jachna obtained his M.Sc. and Ph.D. degrees in Electronic and Communication Engineering from the Military University of *Technology* (MUT) in Warsaw in 1995 and 2003. He is currently an assistant professor at the university, where he teaches students digital technology and conducts research. His research interests focus on the intersection of hardware and software, mainly for precision time and

frequency measurement instruments, where high efficiency of information transfer using standard interfaces such as Ethernet or USB must be ensured. He is also interested in the problems of effective design of digital circuits implemented in FPGA circuits, using hardware languages such as VHDL, and the problems of intra-circuit synchronization.

Jakub Tyburski received the M.Sc. degree in Electronic and Communication Engineering from the Military University of *Technology* (MUT), Warsaw, Poland, in 2017. He is currently a Teaching Assistant at the Faculty of Electronics of MUT, where he is involved in teaching and research. In 2020 he was a member of the team successful in Nokia FPGA Hackathon and Conference, Kraków, Poland. He

serves as a secretary of B.Sc. or M.Sc. thesis defence committies and is also a Ph.D. student. His scientific interests focus on adaptive calibration methods for precise time counters, time-to-digital and frequency-to-digital converters, programmable devices, ASIC-based systems, as well as Artificial Intelligence (AI). He is particularly familiar with modern AI chatbots, including ChatGPT, DeepSeek, Meta AI or Gemini. He has also authored the VHDL-described parametrized design for fast implementation of Feedforward Neural Networks (FNNs) in FPGA devices. His actual work relates to calibration procedures for precise time counters. He has contributed to various research projects referred to precise time metrology, and to papers appearing in scientific journals or conference proceedings.

Pawel Ślązak received the M.Sc. degrees in Electronic and Communication Engineering from the Military University of *Technology* (MUT), Warsaw, Poland, in 2023. He is currently He is currently a second-year PhD student at the Doctoral School of MUT and works at the Faculty of Electronics of MUT, where he is involved in teaching and scientific research. His scientific interests focus

on time metrology and time-to-digital converters.

Albin Czubla received the M. S. degree in theoretical physics, in 1994, and the Ph. D. degree in physics, in 1999, at Maria Curie-Skłodowska University in Lublin, Poland. Since 2002, he works in Time and Frequency Laboratory at Central Office of Measures, Warsaw, Poland. Actually, he is a D-ty Director of Time and Length Department and a head of Time and Frequency Laboratory, a representative of Poland in TCTF EURAMET and CCTF of

CIPM, technical expert in time and frequency metrology for accreditation body. His research interests are maintenance of atomic time scales, stability analysis of time and frequency signals, precise time interval measurements, development of measurement methods and measurement uncertainty analysis.